2025年10月21日,浙江大学硅及先进半导体材料全国重点实验室杨德仁院士、孙威长聘副教授、集成电路学院徐杨教授合作在Cell Press细胞出版社期刊Cell Reports Physical Science发表题为“Bridging machine learning and neuroscience with a silicon nanosheet neuromorphic device”的研究成果。他们利用设计了基于SiNS器件的原型计算芯片,该脉冲神经网络(SNN)器件展现出与生物神经系统类似的行为,并具备片上模式识别能力。此外,团队还与新加坡国立大学Aaron V. Y. Thean团队合作,在Device期刊发表文章:Tunable volatile and nonvolatile switching in silicon nanosheets memristor array for reservoir computing,展示了一种易失性和非易失性可调的硅纳米片忆阻器阵列,并用于储层计算领域。

机器学习是一门起源于神经科学的历史性学科,近年来取得了显著的进展。大型语言模型(LLMs)已成为技术前沿的代表,并被广泛集成到各种终端设备中。尽管机器学习取得了令人瞩目的成功,但其中仍存在一些尚待解决的根本性问题。

但机器学习中神经网络规模的爆炸式增长引出了另一个问题:是否存在比现有计算系统更适合神经网络或神经科学研究的计算架构?大型语言模型的惊人能力在很大程度上源于其庞大的参数规模。然而,随着摩尔定律逐渐逼近极限,芯片器件的微缩也接近物理边界。晶圆制程的持续升级已无法跟上参数量的爆发式增长,这使得模型计算负担极为沉重,阻碍了隐私敏感用户或独立研究团队在本地平台上的部署与应用。

本研究旨在构建一个可行的半导体芯片平台,用于神经科学与机器学习的交叉研究。从神经科学角度看,晶体管为基础的数字电路并非为直接模拟神经元膜电位的模拟信号而设计;而从机器学习角度看,冯·诺依曼架构中的分层存储与缓存机制在大规模并行计算时会导致数据吞吐与运算速度之间的固有矛盾。由于存储与计算分离,神经权重等数据需频繁加载,严重限制了计算效率。这为设计创新计算范式提供了契机——通过引入新材料、新器件及新型体系结构,有望实现理想的“存算一体”架构。

然而,传统的硅基CMOS技术往往难以以紧凑和节能的方式复制神经形态特征。新兴材料如铁电材料、钙钛矿材料、二维(2D)材料等,虽然被应用于忆阻器件,但往往存在CMOS兼容性差和生产成本高的问题。此外,两种类型(易失性和非易失性)忆阻器所用材料的差异也带来了加工复杂性和潜在的集成障碍。硅纳米片(Si NSs)是块状硅的层状薄结构,具有与块状硅不同的物化特性,同时与成熟的硅基工艺具有潜在的兼容性。与SiO2或块状晶体硅相比,Si NSs独特的2D结构提供了丰富的性能可调性,使其成为下一代电子的应用平台。

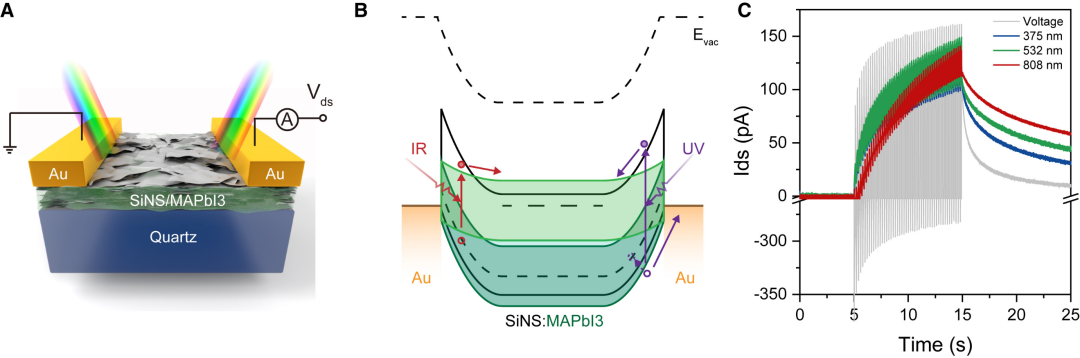

图1.硅纳米片神经形态器件。

在Cell Reports Physical Science的工作中,设计了基于SiNS器件的原型计算芯片。作为一种潜在的新型计算单元,SiNS器件能够原位实现模拟突触后电位的“存算一体”计算,避免了传统缓存过程中的延迟。该脉冲神经网络(SNN)器件展现出与生物神经系统类似的行为,并具备片上模式识别能力。通过将器件的可调特性与人工神经网络的数学模型相结合,我们建立了神经响应、器件行为与ANN模型之间的紧密对应关系。研究揭示了深层SNN与ANN之间的映射关系,以及SNN层间的准ReLU(修正线性单元)关系,使得能够构建“代理ANN”模型。将预训练代理ANN的参数(忽略具体脉冲时间信息)转移至SNN后,模型仍能实现高精度的模式识别。此后,通过结合时间信息的脉冲神经网络专用“替代梯度算法”(surrogate gradient algorithm)进行联合训练(tandem learning),网络性能得到进一步优化。这种交互式的联合学习过程揭示了神经科学与机器学习之间可能存在的深层联系。

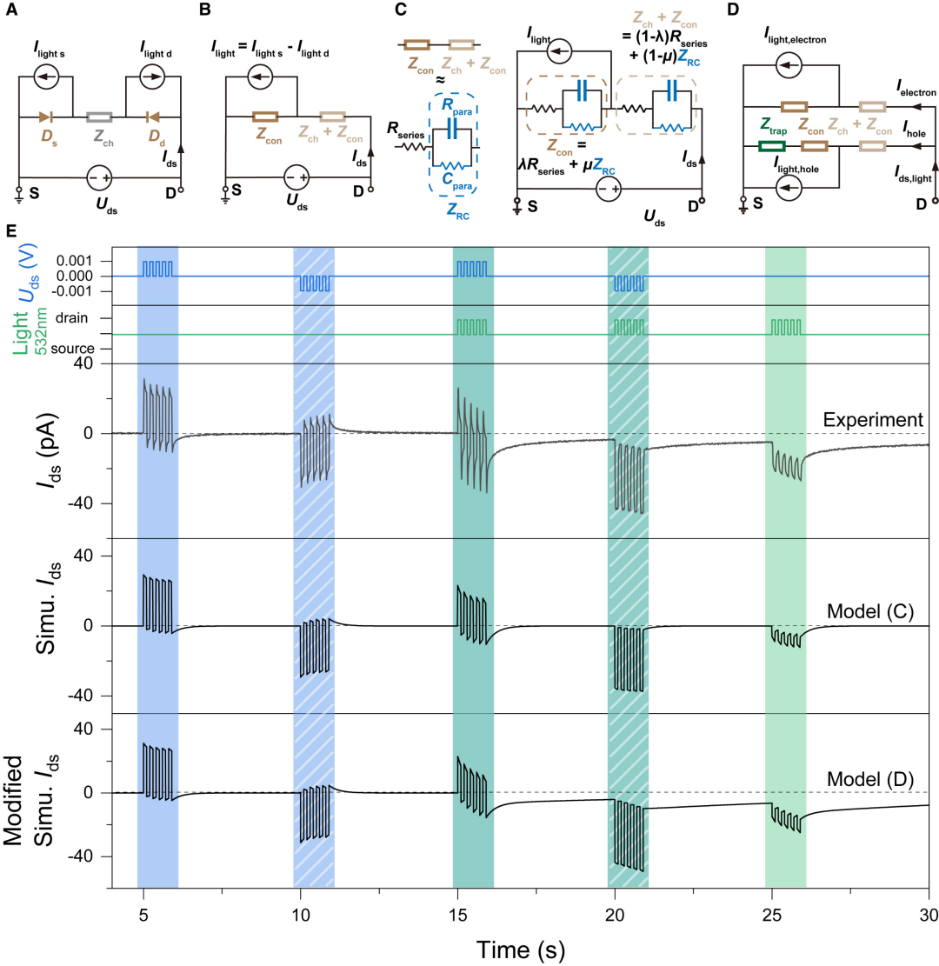

图2. SiNS器件的理论建模与实验验证。

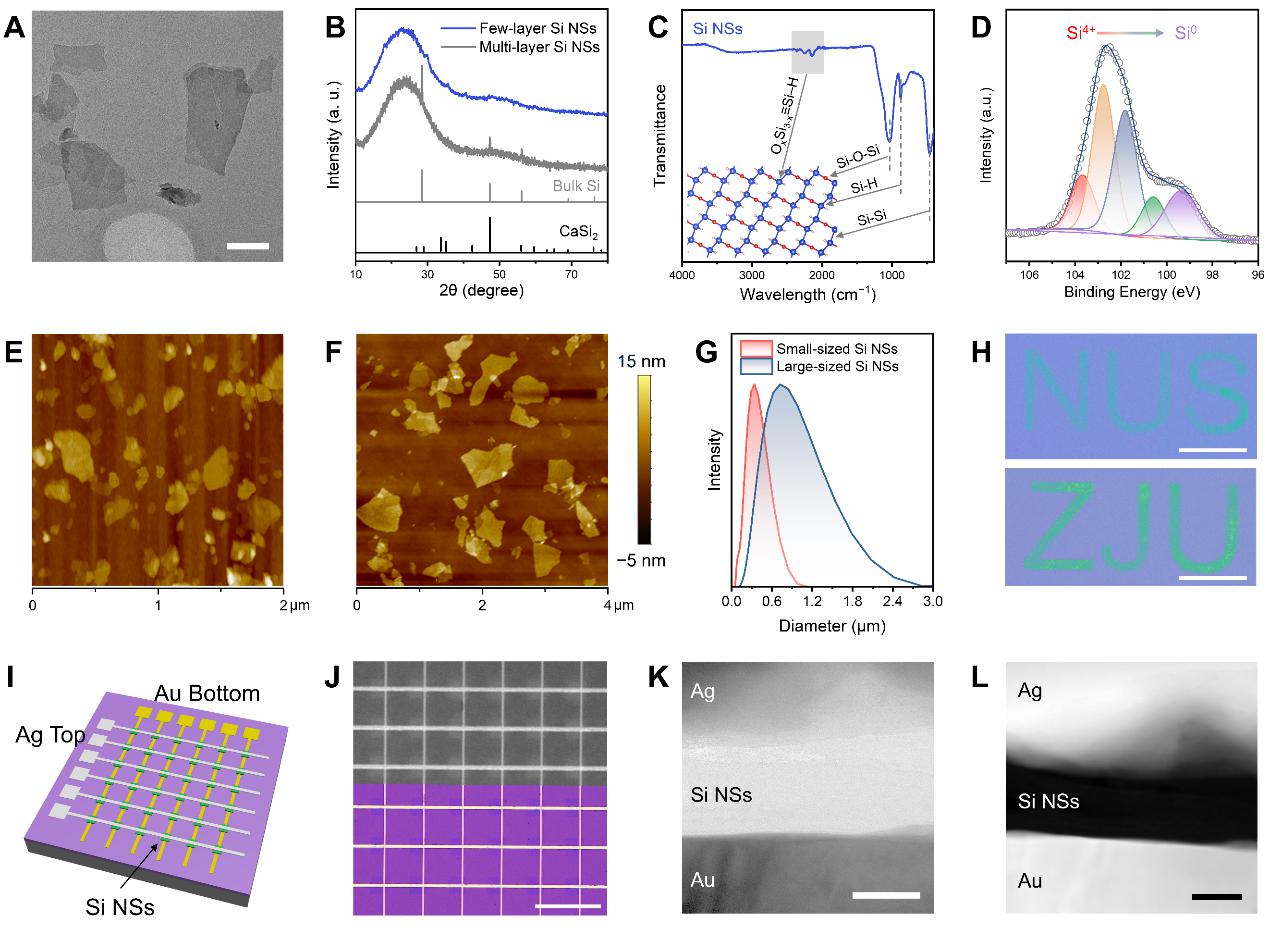

在Device的工作中,介绍了一种基于少层硅纳米硅忆阻器的储层计算处理器。我们通过硅化钙(CaSi2)的层间膨胀液相剥离,经部分自发氧化生成硅氧烷结构,合成了高纯度、平均厚度为5.6nm的少层Si NSs。随后,通过室温自组装工艺将均匀的Si NSs薄膜沉积在预图案电极上,以可扩展和CMOS兼容的方式形成垂直的6 × 6 Ag/Si NSs/Au忆阻器交叉阵列。交叉阵列具有2 × 2μm2的微型器件尺寸,使其非常适合高集成密度应用。

图3.少层硅纳米片和忆阻器交叉阵列的制造策略

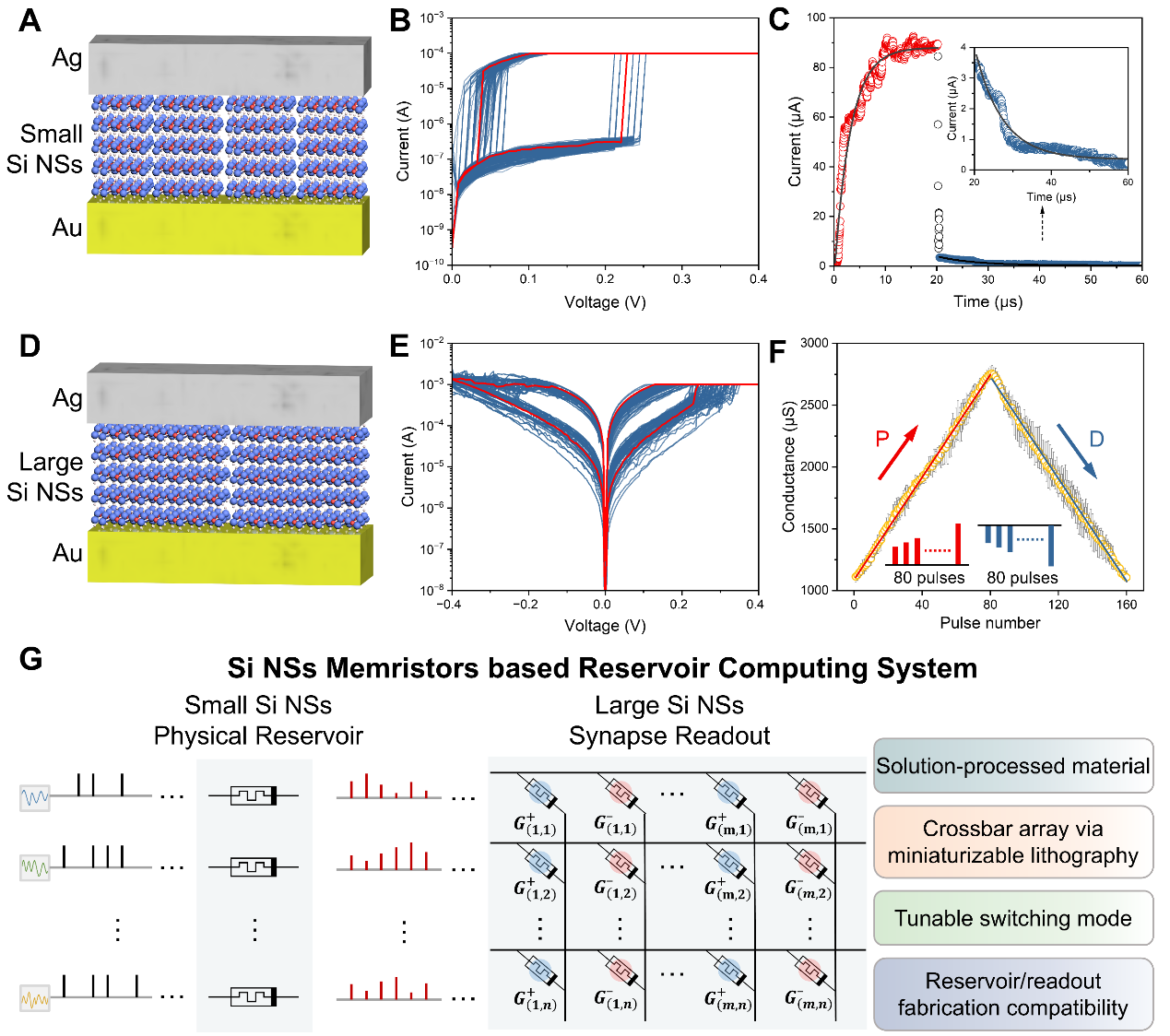

Si NSs忆阻器表现出易失性或非易失性开关行为,由纳米片的横向尺寸调节。小尺寸的Si NSs具有低设定电压(0.23 V)、对电压脉冲的非线性瞬态响应、4位顺序输入的可区分输出等特点,适合储层使用。相比之下,大尺寸的Si NSs具有非易失性模拟RS行为,超低的设置/复位电压(0.24 V/−0.18 V),电导更新的良好线性度,以及稳定的电阻保留时长,可以用作读出层的突触。包括导电原子力显微镜(C-AFM)和密度泛函理论(DFT)计算在内的物理分析表明,Si NSs中的边缘缺陷促进了Ag+的层间扩散,调节了导电丝的动力学并产生了双模式切换行为。利用这种独特的双模式功能,我们实现了基于Si NSs忆阻器的集成储层计算处理器,该处理器在时间数据处理方面具有很高的准确性,并通过MNIST手写数字识别和二阶非线性动力学预测得到了验证。这项工作为实现基于硅的技术实现紧凑和节能的时间处理器开辟了一条有希望的途径。

图4.硅纳米片忆阻器阵列的电子性能

文章内容均引自《CellPress全科学》公众号