文章部分内容来源于:FUTURE 远见 原文选编闵青云

近年来,随着芯片制程逐渐逼近物理极限,面对硅材料的固有限制,芯片先进工艺尺寸微缩如何继续?芯片功能如何扩展?而得益于二维(2D)材料的原子级厚度和表面无悬挂键的结构特性、优异的光电及量子效应等,2D材料被广泛认为在后摩尔技术中扮演关键角色。那么,如何充分利用2D半导体来弥补硅基技术的不足?

鉴于此,浙江大学硅材料国家重点实验室徐明生教授、杨德仁院士和复旦大学周鹏教授团队为2D半导体融合于硅基技术提出了单片「硅上」(硅作为基底,On-Silicon)和「与硅」(与硅器件/电路实现功能集成,With-Silicon)概念。聚焦讨论了2D材料合成、器件设计和芯片集成的相应要求,总结了2D材料在以硅为主导的半导体行业中发挥的作用,并提出未来发展方向及未来可能成为主流的技术。相关长文综述以「Two-dimensional devices and integration towards the silicon lines」为题发表于《自然·材料》(Nature Materials)。

【关于文章】

晶体管物理尺寸遵循登纳德(Dennard)缩放比例,并随着掺杂复杂性和栅极漏电而达到顶峰,随后在架构迭代和优化方面做出努力,以减轻短沟道效应。

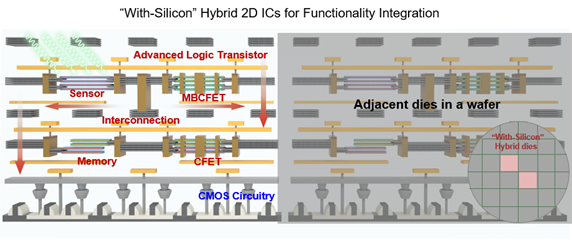

在鳍式晶体管(FinFET)取得显著成功之后,最先进的新架构如多桥沟道晶体管(MBCFET)和互补型晶体管(CFET)相继出现进一步延续摩尔定律。

然而,体硅表面和内部缺陷不可避免地导致载流子迁移率在亚4 纳米后出现急剧下降。尽管技术在不断进步,但固有的晶格和量子隧穿限制意味着硅材料微缩在可预见的未来将走向尽头。

2D 半导体无悬挂键的钝化表面能够将散射效应降到最低,保证了原子级薄层下迁移率不发生退化。此外,短沟道器件的电流密度与90 纳米节点的应力硅晶体管电流密度相当,接近国际器件和系统路线图的高性能和低功耗2028年目标。当下2D 材料已不仅仅在学术界具有极大的研究价值,英特尔、台积电、IMEC等半导体巨头也纷纷布局。然而,在硅主导的半导体行业中,2D 器件与电路的发展仍然缺乏明确和统一的方向。例如大多数2D 器件和电路只使用硅晶圆作为衬底,而没有真正做到与硅技术的集成。 鉴于硅技术成熟度,以及2D 材料与硅产线前道(FEOL)和后道(BEOL)工艺的兼容性,将它们异质融合到现有硅产线,实现与硅技术功能集成是一种有前景的方案。

图. 基于二维半导体的「与硅」混合集成芯片

【亮点展望】

本工作重点介绍了与硅技术相结合的里程碑式工作,从用于异质光子ICs的2D 光电子器件到在硅产线上实现的晶圆级2D 晶体管;在芯片方面全面回顾了现阶段的单片「On-Silicon」和「With-Silicon」进展。并对推向产线所需的晶圆级2D材料合成、器件设计、芯片集成的要求和可行方案进行了讨论。最后在总结中对2D 材料正在发挥的作用和未来的主流方向进行了展望,包括作为「On-Silicon」风洞平台引导硅技术向More Moore发展,及利用「With-Silicon」混合集成为新兴的More than Moore应用包括成像、神经拟态、全光计算等扩展功能。以新材料、新器件为基础的先进芯片研究中,我国处于领先地位,科研力量充足和积累丰富,如在研发投入支持下到2035年有望主导新体系半导体技术。

【论文链接】

https://www.nature.com/articles/s41563-022-01383-2#peer-review

DOI:10.1038/s41563-022-01383-2

该工作得到了国家自然科学基金委资助和支持。